M.E. Second Semester (Digital Electronics) (Part Time / Full Time) (C.G.S.- New)

## 13232 : Parallel Computing : 2 UMEF 3 / 4 UMEP 1

P. Pages: 2

AW - 3764

Max. Marks: 80

7

7

7

6

Time: Three Hours

Notes: 1. Due credit will be given to neatness and adequate dimensions.

- 2. Assume suitable data wherever necessary.

- 3. Illustrate your answer necessary with the help of neat sketches.

- 4. Use of pen Blue/Black ink/refill only for writing the answer book.

- 1. a) Give Flynn's classification of various computer architectures. Clearly explain the features of each with conceptual diagrams.

- b) A 40 MHz processor was supposed to execute 200000 instructions with following instruction mix and CPI needed for each instruction. Determine the effective CPI, MIPS rate and execution time.

| Instruction type   | CPI | Instruction count |

|--------------------|-----|-------------------|

| Integer arithmetic | 2   | 60%               |

| Data transfer      | 4   | 18%               |

| Floating point     | 6   | 12%               |

| Control transfer   | 5   | 10%               |

OR

- 2. a) Differentiate between implicit and explicit parallelism with a neat sketch.

- b) Explain different types of data dependency with an example. Draw the data dependency graph for the following.

S1: Load R1, M(200)

S2: Move R2, R1

S3: Inc R1

S4: Add R2, R1

S5: Store M(200), R1

Explain how grain packing can be done to compute the sum of the 4 elements in the resulting product matrix  $C = A \times B$ . Where A and B are  $2 \times 2$  matrices. Assume grain size for multiplication is 101 and the grain size for addition is 8.

OR

4. a) Compare control flow verses dataflow mechanism with necessary diagram.

b) Explain the following static connection networks.

i) Linear Array ii) Binary flat tree and iii) Hyper cube

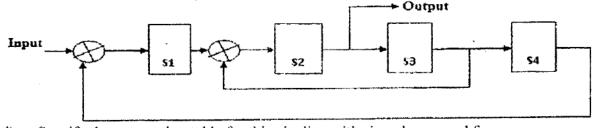

5. Consider the following pipelined processor with four stages. This pipeline has a total evaluation time of six clock cycles. All successor stages must be used after each clock cycle.

- i) Specify the reservation table for this pipeline with six columns and four rows.

- ii) List the set of forbidden latencies between task initiations.

|     |                                                                                                       | <ul> <li>iii) Draw the state diagram which shows all possible latency cycles.</li> <li>iv) List all greedy cycles from the state diagram.</li> <li>v) What is the value of minimal average latency (MAL)?</li> </ul> OR |   |  |

|-----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| 6.  |                                                                                                       | Differentiate between:  i) Super scalar processors and VLIW processors.  ii) Trace scheduling and dynamic scheduling.  iii) Software pipelining and hardware pipelining.                                                |   |  |

| 7.  | a)                                                                                                    | What is the cache coherence and why is it important in shared memory multiprocessor system? How can the problem be solved with snoopy cache controller?                                                                 |   |  |

|     | b)                                                                                                    | What do you mean by virtual channels? Explain in brief the deadlock avoidance techniques.                                                                                                                               | 7 |  |

|     |                                                                                                       | OR                                                                                                                                                                                                                      |   |  |

| 8.  | a)                                                                                                    | Explain in brief the following directory based protocols.  i) Full map directories.  ii) Limited directories.                                                                                                           | 7 |  |

|     | b)                                                                                                    | Explain in brief the Goodman's write once cache coherence protocol.                                                                                                                                                     | 7 |  |

| 9.  | a)                                                                                                    | Distinguish between.  i) Multiprocessor and Hyperthreading technology.  ii) Hardware based and software based multithreading.                                                                                           | 8 |  |

|     | b) Discuss the features of message driven processor, making it suitable for building f multicomputer. |                                                                                                                                                                                                                         |   |  |

|     |                                                                                                       | OR                                                                                                                                                                                                                      |   |  |

| 10. | a)                                                                                                    | Discuss the effect of using a relaxed consistency memory model in a scalable multiprocessor with multi threading.                                                                                                       | 7 |  |

|     | b)                                                                                                    | What do you mean by efficiency of a processor. Discuss in brief the processor efficiency in i) Saturation region.                                                                                                       | 6 |  |

| 11. | a)                                                                                                    | Explain the following as applied to parallel programming environment.  i) Visualization support. ii) Performance tuning.                                                                                                | 7 |  |

|     | b)                                                                                                    | Differentiate between passing programming model and shared memory programming model.  OR                                                                                                                                | 6 |  |

| 12. | a)                                                                                                    | Discuss synchronization mechanism for inter-process communication with the help of basic operation.                                                                                                                     | 7 |  |

|     | b)                                                                                                    | Discuss in brief as applied to multi-processing environment.  i) Multitasking ii) Auto - tasking.                                                                                                                       | 6 |  |

|     |                                                                                                       |                                                                                                                                                                                                                         |   |  |

\*\*\*\*\*\*

AW - 3764